多芯片集成電路設(shè)計(jì) 揭秘50個(gè)半導(dǎo)體芯片的協(xié)同場(chǎng)景圖

在現(xiàn)代電子科技的浩瀚星空中,多芯片集成電路(Multi-Chip Integrated Circuit,簡(jiǎn)稱MCIC)猶如一幅精密而宏大的微縮景觀圖,將數(shù)十乃至上百個(gè)半導(dǎo)體芯片的功能與性能,凝聚于一方寸之間。當(dāng)我們將視角聚焦于一幅包含50個(gè)半導(dǎo)體芯片的場(chǎng)景圖時(shí),所見不僅是物理上的排列組合,更是一場(chǎng)關(guān)于集成度、異構(gòu)計(jì)算、系統(tǒng)級(jí)設(shè)計(jì)與未來(lái)應(yīng)用的前沿探索。

一、 場(chǎng)景圖構(gòu)成:從宏觀布局到微觀互聯(lián)

一幅典型的50芯片多芯片集成電路橫版場(chǎng)景圖,在視覺上首先呈現(xiàn)的是一種高度有序的模塊化布局。它并非簡(jiǎn)單的堆疊,而是根據(jù)功能分區(qū)、信號(hào)流與功耗熱管理進(jìn)行精心規(guī)劃。

- 核心計(jì)算集群:場(chǎng)景中央或特定區(qū)域,通常會(huì)集中布置高性能CPU、GPU或?qū)S肁I加速器芯片(如NPU、TPU)。這些芯片可能采用最先進(jìn)的制程工藝,負(fù)責(zé)處理最復(fù)雜的計(jì)算任務(wù)。它們之間通過(guò)超高帶寬的片間互連(如硅中介層中的微凸塊連接)緊密耦合,以實(shí)現(xiàn)內(nèi)存一致性或低延遲數(shù)據(jù)交換。

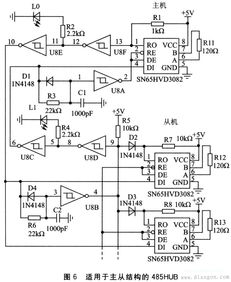

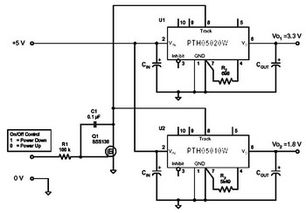

- 專用功能島嶼:圍繞著核心計(jì)算單元,分布著各種專用芯片,如高速SerDes(串行器/解串器)芯片用于外部高速通信(PCIe, Ethernet),內(nèi)存控制器芯片(管理HBM堆棧),電源管理芯片(PMIC)負(fù)責(zé)精準(zhǔn)的電壓調(diào)節(jié)與功耗分配,以及射頻(RF)芯片、傳感器接口芯片等。每個(gè)“島嶼”都是一個(gè)功能完備的子系統(tǒng)。

- 存儲(chǔ)矩陣:高帶寬內(nèi)存(HBM)芯片通常以2.5D或3D方式堆疊在邏輯芯片附近,通過(guò)硅通孔(TSV)互聯(lián),形成垂直的存儲(chǔ)支柱。圖中可能顯示多個(gè)HBM堆棧,像衛(wèi)兵一樣矗立在計(jì)算核心旁,提供海量且高速的數(shù)據(jù)供給。

- 互聯(lián)網(wǎng)絡(luò)與中介層:所有芯片并非直接焊接在基板上,而是通過(guò)一個(gè)無(wú)源的硅中介層或有機(jī)再布線層(RDL)實(shí)現(xiàn)互連。場(chǎng)景圖中,這些互連布線如同密集的“高速公路網(wǎng)”和“市內(nèi)道路”,以微米級(jí)的線條在芯片下方縱橫交錯(cuò),承擔(dān)著數(shù)據(jù)、指令和電力的傳輸重任。

- 封裝與散熱結(jié)構(gòu):橫圖視角下,封裝外殼(可能為扇出型封裝或2.5D/3D封裝結(jié)構(gòu))的輪廓清晰可見。散熱蓋(IHS)、熱界面材料(TIM)以及下方可能集成的微流道冷卻結(jié)構(gòu),共同構(gòu)成了管理這50顆芯片所產(chǎn)生巨大熱量的關(guān)鍵系統(tǒng)。

二、 設(shè)計(jì)哲學(xué):異構(gòu)集成與系統(tǒng)級(jí)優(yōu)化

設(shè)計(jì)如此復(fù)雜的多芯片集成電路,其核心思想是 “異構(gòu)集成” 與 “系統(tǒng)級(jí)協(xié)同” 。

- 超越摩爾定律:當(dāng)單一芯片的制程微縮逼近物理極限,通過(guò)將不同工藝節(jié)點(diǎn)、不同材料、不同功能的芯片(如模擬、數(shù)字、射頻、光電子)集成在一個(gè)封裝內(nèi),成為持續(xù)提升系統(tǒng)性能、降低功耗和成本的有效路徑。圖中50個(gè)芯片可能分別采用7nm、12nm甚至更成熟的制程,各取所長(zhǎng)。

- 芯片即“樂高”:這種設(shè)計(jì)模式類似于用已知的、驗(yàn)證過(guò)的“芯片IP”進(jìn)行系統(tǒng)級(jí)搭建。設(shè)計(jì)者可以混合搭配來(lái)自不同供應(yīng)商的最佳芯片(如英特爾的CPU、英偉達(dá)的GPU、三星的HBM、博通的網(wǎng)絡(luò)芯片),快速構(gòu)建面向特定應(yīng)用(如數(shù)據(jù)中心AI訓(xùn)練、自動(dòng)駕駛、高端通信設(shè)備)的定制化解決方案。

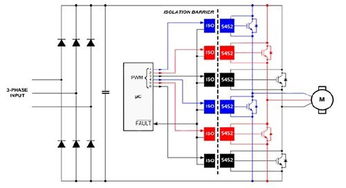

- 互連技術(shù)是關(guān)鍵:場(chǎng)景圖中的芯片間互連帶寬和延遲,直接決定了整體系統(tǒng)性能。先進(jìn)封裝技術(shù)(如臺(tái)積電的CoWoS、英特爾的EMIB、Foveros)使得芯片間互連密度和能效比傳統(tǒng)PCB板級(jí)連接高出數(shù)個(gè)量級(jí),實(shí)現(xiàn)了近乎單芯片般的通信效率。

- 功耗與熱管理的頂層設(shè)計(jì):50顆芯片同時(shí)工作,峰值功耗可能高達(dá)數(shù)百甚至上千瓦。因此,電源傳輸網(wǎng)絡(luò)(PDN)的設(shè)計(jì)和芯片的功耗分布圖在規(guī)劃初期就必須協(xié)同考慮。場(chǎng)景圖中,高功耗芯片可能被刻意分開布局,并與散熱結(jié)構(gòu)直接對(duì)準(zhǔn),避免形成局部熱點(diǎn)。

三、 應(yīng)用場(chǎng)景與未來(lái)展望

擁有50個(gè)芯片的復(fù)雜多芯片集成電路,主要瞄準(zhǔn)的是對(duì)算力、帶寬和能效有極致要求的領(lǐng)域:

- 人工智能與高性能計(jì)算:用于訓(xùn)練超大規(guī)模神經(jīng)網(wǎng)絡(luò),處理科學(xué)計(jì)算模擬。

- 數(shù)據(jù)中心與云計(jì)算:作為服務(wù)器核心,提供強(qiáng)大的通用與專用計(jì)算能力。

- 先進(jìn)通信與網(wǎng)絡(luò):在5G/6G基站、核心路由設(shè)備中實(shí)現(xiàn)高速信號(hào)處理與交換。

- 自動(dòng)駕駛與邊緣計(jì)算:在有限的空間和功耗預(yù)算下,集成感知、決策、控制等多種功能單元。

這幅“50芯片場(chǎng)景圖”還將繼續(xù)演化:

- 向3D立體集成邁進(jìn):芯片將從“并肩作戰(zhàn)”走向“疊羅漢”,通過(guò)芯片堆疊實(shí)現(xiàn)更短的互連和更高的集成密度。

- 光互連與新型材料的引入:在芯片間或芯片內(nèi)引入硅光引擎,用光信號(hào)替代部分電信號(hào),以突破帶寬和功耗瓶頸。

- 更智能的芯粒(Chiplet)生態(tài)系統(tǒng):標(biāo)準(zhǔn)化的芯粒接口協(xié)議(如UCIe)將成熟,使得來(lái)自不同廠商的芯粒能像拼圖一樣無(wú)縫組合,這幅場(chǎng)景圖的構(gòu)建將更加靈活和標(biāo)準(zhǔn)化。

###

一幅包含50個(gè)半導(dǎo)體芯片的多芯片集成電路橫圖,是當(dāng)代集成電路設(shè)計(jì)巔峰技藝的縮影。它不再僅僅追求晶體管的數(shù)量,而是升維到了系統(tǒng)架構(gòu)、異構(gòu)集成、先進(jìn)封裝和軟硬件協(xié)同的全新戰(zhàn)場(chǎng)。在這幅微縮的科技景觀中,每一顆芯片都是一個(gè)功能節(jié)點(diǎn),每一條互連線都是數(shù)據(jù)血脈,共同編織出驅(qū)動(dòng)數(shù)字世界向前發(fā)展的強(qiáng)大引擎。解讀這幅圖,便是解讀下一代計(jì)算系統(tǒng)的核心藍(lán)圖。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.kuanghuai.cn/product/58.html

更新時(shí)間:2026-01-07 08:23:58