Lexar雷克沙攜手慧榮科技亮相CES 2024,移動固態硬盤新品與“妙傳索思”平臺引領存儲新體驗

在2024年國際消費電子展(CES)的璀璨舞臺上,存儲解決方案領域的領先品牌Lexar雷克沙與主控芯片大廠慧榮科技(Silicon Motion)聯合“重拳出擊”,帶來了一場技術與創新的雙重盛宴。此次合作不僅展示了雙方在高端存儲技術上的深厚積累,更通過一系列新品和前瞻性平臺,為消費者和專業用戶描繪了未來數據存儲與傳輸的嶄新圖景。

一、 新品亮相:速度、容量與設計的全面進化

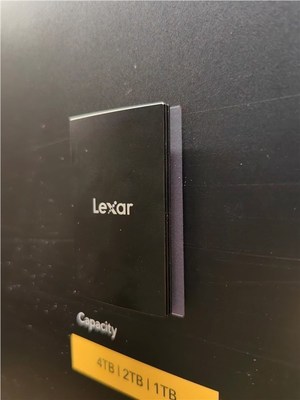

Lexar雷克沙此次推出的移動固態硬盤新品無疑是展會的焦點之一。這些產品搭載了慧榮科技提供的先進主控芯片解決方案,在性能上實現了顯著突破。據悉,新品在讀寫速度上達到了新的高度,能夠輕松應對4K/8K超高清視頻素材的實時編輯、大型游戲的快速加載以及海量數據的高速備份等嚴苛需求。產品在容量上也提供了更豐富的選擇,滿足從日常辦公到專業內容創作的不同層級需要。

除了內在性能,新品在外觀設計和耐用性上也下足了功夫。采用堅固輕巧的材質,兼顧了便攜性與抗沖擊能力,部分型號還可能具備防水防塵特性,適應各種復雜的使用環境。其緊湊的設計和時尚的外觀,使其不僅是強大的數據存儲工具,也成為了科技愛好者隨身裝備中的亮眼配件。

二、 技術內核:慧榮科技主控芯片的強力驅動

新品卓越性能的背后,離不開慧榮科技先進主控芯片的強力支持。作為全球知名的NAND閃存主控芯片供應商,慧榮科技提供了高性能、低功耗、高可靠性的芯片解決方案。此次合作中采用的芯片,支持最新的接口協議(如USB 3.2 Gen 2x2等),并優化了數據傳輸算法,確保了存儲設備在高速讀寫狀態下的穩定性和數據完整性。這種強強聯合,使得Lexar雷克沙移動固態硬盤在激烈的市場競爭中,具備了堅實的核心技術優勢。

三、 平臺賦能:“妙傳索思知食平臺”構想未來智能存儲生態

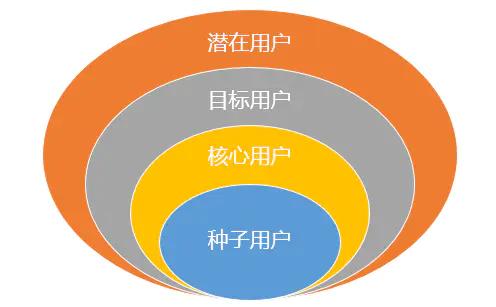

更具前瞻性的是,此次亮相還提及了“妙傳索思知食平臺”這一概念。雖然平臺具體細節有待進一步公布,但從名稱和語境可以推斷,這很可能是一個超越單純硬件,融合了智能數據管理、快速內容分享(“妙傳”)、知識或內容組織(“索思”)、甚至可能結合特定垂直領域(如“知食”可能暗示與美食內容創作或管理相關)服務的綜合性軟件或云端生態系統。

該平臺的設想,標志著Lexar雷克沙正從硬件制造商向“硬件+軟件+服務”的綜合解決方案提供商轉型。它旨在解決用戶在數據爆炸時代面臨的痛點——不僅僅是存儲空間和速度,更是數據的管理、分類、檢索和安全分享。例如,攝影師可以快速將拍攝的原始素材通過移動硬盤智能歸類并生成預覽;視頻團隊可以無縫協作分享大型工程文件;美食博主可以高效管理海量的食譜圖片與視頻素材。

四、 CES 2024的啟示:存儲的未來是融合與智能

Lexar雷克沙與慧榮科技在CES 2024上的這次聯合展示,清晰地揭示了移動存儲市場的發展趨勢:

- 性能競賽持續:更高的速度、更大的容量、更堅固的設計仍是基礎。

- 產業鏈協同深化:品牌商與上游芯片供應商的緊密合作,是推出標桿性產品的關鍵。

- 生態化體驗升級:單一的硬件產品已無法滿足全方位需求,與之配套的智能軟件和增值服務正成為新的競爭高地。“妙傳索思知食平臺”的構想正是這一趨勢的體現。

通過此次CES大展,Lexar雷克沙與慧榮科技不僅“重拳出擊”展示了硬核的移動固態硬盤新品,更以“妙傳索思知食平臺”的概念拋出了關于未來智能存儲生態的橄欖枝。這不僅是兩款新產品,更是一套關于高效、智能、互聯數據生活方式的提案。隨著這些產品和服務的逐步落地,用戶將能享受到從物理存儲到數據價值管理的全鏈路優質體驗,預示著個人與專業數據存儲領域一個更加高效、智能的新時代正在到來。

如若轉載,請注明出處:http://www.kuanghuai.cn/product/27.html

更新時間:2026-04-08 02:32:58